728x90

반응형

경희대학교 김정욱 교수님의 컴퓨터구조 강의를 기반으로 정리한 글입니다.

Common Framework for Memory Hierarchy

- TLB는 virtual address만 → 실제 data를 포함한 L1보다 용량이 작음

- 용량이 클수록 miss rate 감소

Block Placement of Memory Hierarchy

Where Can a Block Be Placed?

- direct mapped, fully associative는 set associative의 일종

- 자유도 증가 → miss rate 감소

- cache size 증가 → miss rate 감소

- 자유도 증가 → block 교체 확률 감소 → miss rate 감소

- but, 자유도가 너무 크면 → saturation됨

- cache size 증가 → 자유도 영향 감소

How is a Block Found?

Which Block Should Be Replaced on a Cache Miss?

- Direct-mapped cache: set에 존재하는 하나의 block이 교체 후보

- Set associative: set에 존재하는 자유도만큼의 block이 교체 후보

- Fully associative: 모든 block이 교체 후보

- Least Recently Used(LRU): Reference Bit를 통해 가장 오래 사용되지 않은 block 교체

- Random: 후보 block 중 무작위 선택

- 자유도가 큰 경우 → LRU 근사 사용 or Random

- LRU 근사: 작은 miss rate 감소도 miss가 발생했을 때 디스크에 접근하는 손해가 크기에 중요

What Happens on a Write?

Write-through

- cache에 저장될 때마다, memory에 바로 write

- write-back보다 구현이 쉬움

Write-back

- cache에만 정보가 저장되고, 수정된 block이 교체될 때만 memory에 반영

Virtual memory

- write-back만 쓰임

- disk에 매번 접근하는 것은 오래 걸림

Source of Misses

Compulsory misses(=cold-start misses)

- cache에서 해당 block이 한 번도 접근된 적 없을 때 발생

Capacity misses

- cache의 용량이 가득 차서 발생

- cache size를 키우면 됨

Conflict misses(=collision misses)

- 하나의 set이 가득 차서 발생

- 캐시 공간이 남아도 자유도 때문에 발생하는 miss

- 자유도를 키우면 됨

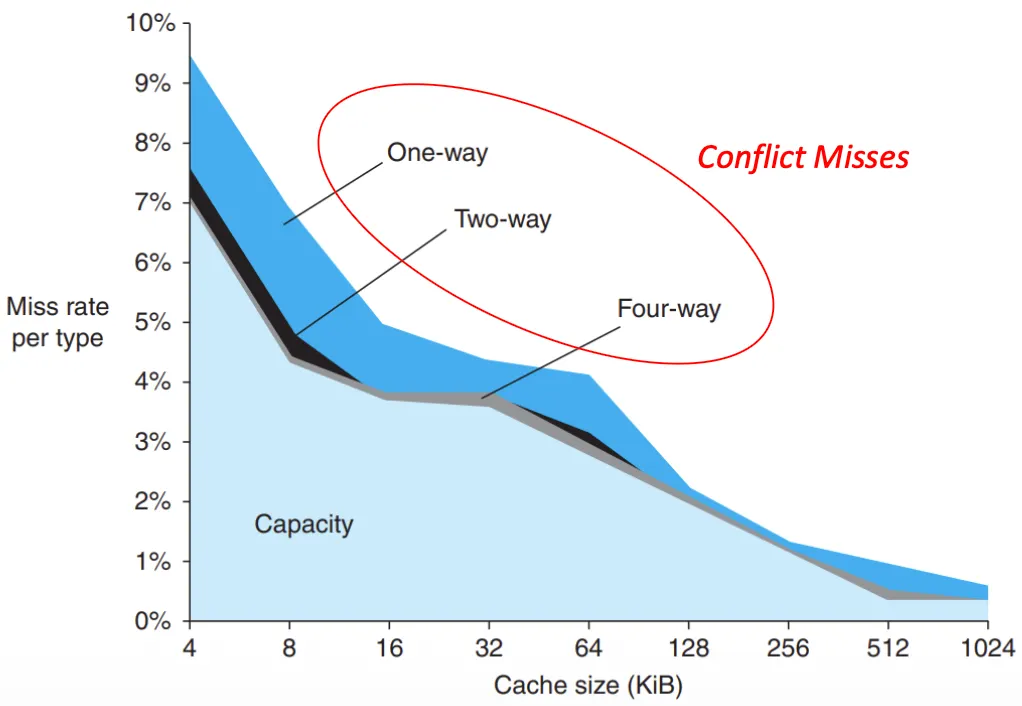

Miss rate per three type of misses

- Capacity misses: 용량 커질수록 miss rate 감소

- Conflict misses: 자유도 커질수록 miss rate 감소

Challenges of Memory Hierarchy Design

- Cache Size: Miss rate vs. Access time

- Associativity: Miss rate vs. Access time

- Block size: Miss rate vs. Miss penalty

Increases cache size

- capacity misses 감소

- access time 증가

Increases associativity

- conflict misses 감소

- access time 증가

Increases block size

- spatial locality → miss rate 감소

- large size block → miss penalty 증가

728x90

반응형

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조] Lecture 18: Memory Hierarchy - Part2 (0) | 2026.02.12 |

|---|---|

| [컴퓨터구조] Lecture 17: Memory Hierarchy - Part1 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 15: The Processor - Part4 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 14: The Processor - Part3 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 13: The Processor - Part2 (0) | 2026.02.12 |