728x90

반응형

경희대학교 김정욱 교수님의 컴퓨터구조 강의를 기반으로 정리한 글입니다.

ROM vs. RAM

ROM(Read Only Memory)

- 읽기만 가능

- Non-volatile memory(비휘발성 메모리): 전원이 꺼져도 영구적으로 파일을 저장

- Mask ROM: 반도체 생산 공정인 마스킹 단계에서 고정된 데이터 회로 패턴으로 생산하는 방식

RAM(Random Access Memory)

- 일시적 메모리

- Read-write memory: 읽고 쓰기 가능

- Volatile memory(휘발성 메모리): 컴퓨터가 동작 중일 때 일시적으로 파일을 저장

- ex. DRAM, SRAM

SRAM vs. DRAM

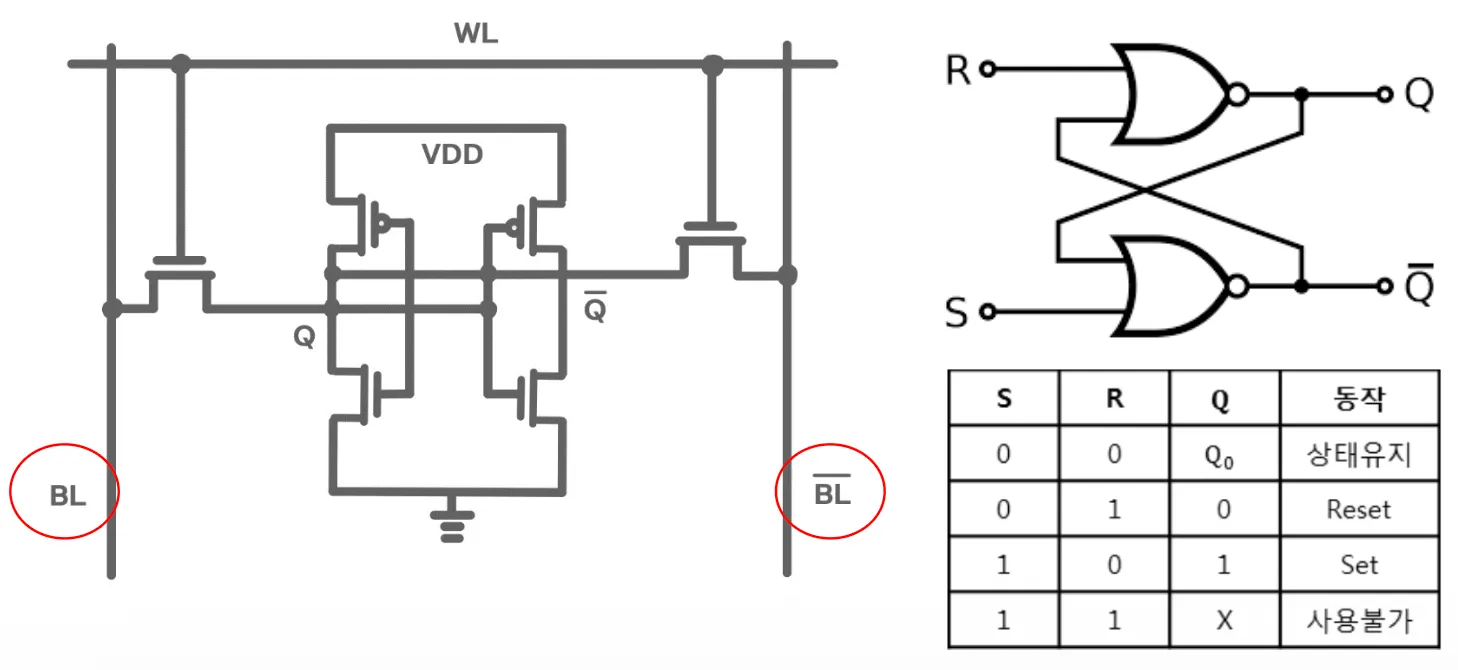

SRAM(Static Random Access Memory)

- cache memory(캐시 메모리)

- 한 비트 표현을 위해 6개 이상의 트랜지스터 필요: DRAM에 비해 집적도가 낮고, 소비 전력이 큼

- 플립플롭 소자로 구성: 전원이 연결된 동안 내용 계속 유지

- 속도가 빠름: SRAM은 capacitor를 사용하지 않아 refresh(충전)이 필요 없음

DRAM(Dynamic Random Access Memory)

- 커패시터 사용: 시간이 지나면 스스로 방전

- 전원이 계속 공급되더라도 커패시터가 주기적으로 재충전되어야 기억된 내용을 유지할 수 있음

- 회로가 비교적 간단하고 가격이 저렴

- 집적도가 높기 때문에 대용량의 기억장치에 주로 사용

- 전원이 꺼지면 자료를 계속 보존할 수 없음

Memory Hierarchy

Principle of Locality(국소성 원리)

Temporal locality

- 한 번 사용되면 → 다시 사용될 가능성이 높음

Spatial locality

- 접근된 주소와 가까운 주소에 접근할 가능성이 높음

- 단, 메모리가 잘 정돈되어 있다는 가정이 필요

Block

- 복사해오는 정보의 최소 단위

데이터가 upper level에 있는 경우

- hit: upper level(cache)에 데이터가 존재

- hit rate(hit ratio): cache가 적중되는 비율 → 메모리 계층 구조의 성능 척도

- hit time: 데이터가 cache에 존재하는지 확인하는 시간

데이터가 upper level에 없는 경우

- miss: hit되지 못함 → 데이터를 한 번도 부른 적 없거나, 부른 적 있는데 캐시 용량이 작아서 지워짐

- miss rate(miss ratio) = 1 - hit rate

- miss penalty: lower level에서 cache로 block을 교체하는 시간 + cache에서 processor로 block을 전달하는 시간

Cache Memory

Cache

- 메모리 계층 구조에서 CPU와 가장 가까운 단계

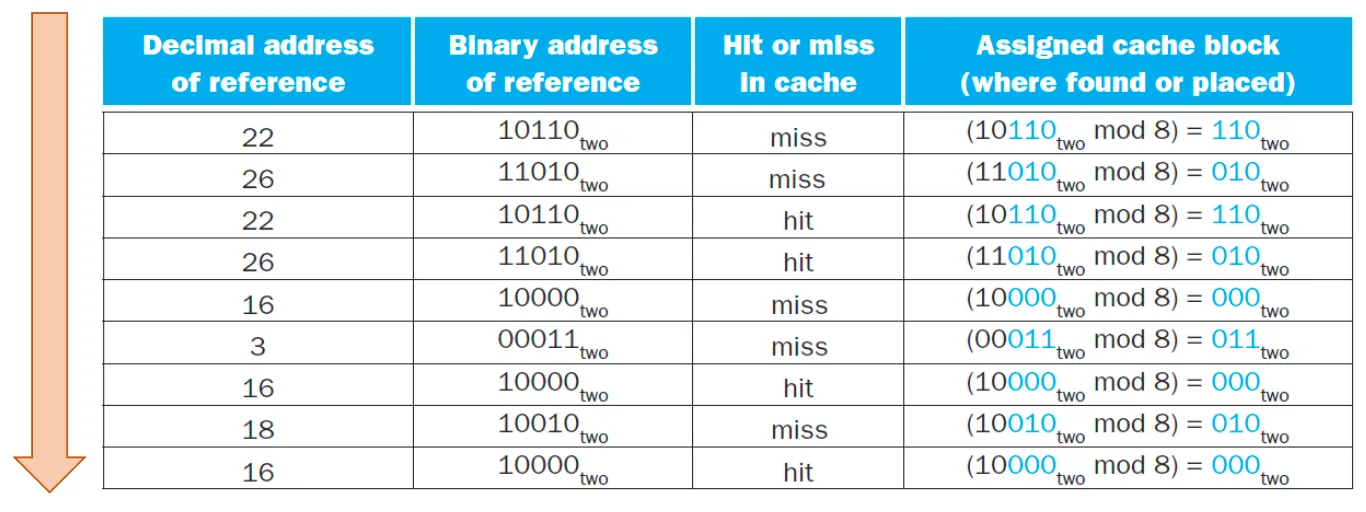

Direct-mapped cache

- 각 메모리 위치가 캐시의 정확히 한 위치에 매핑되는 구조 → modulo 연산

- 메모리 주소는 5bits, cache는 3bits

- 메모리 주소에 대해 3bits(2^3 = 8) modulo 연산

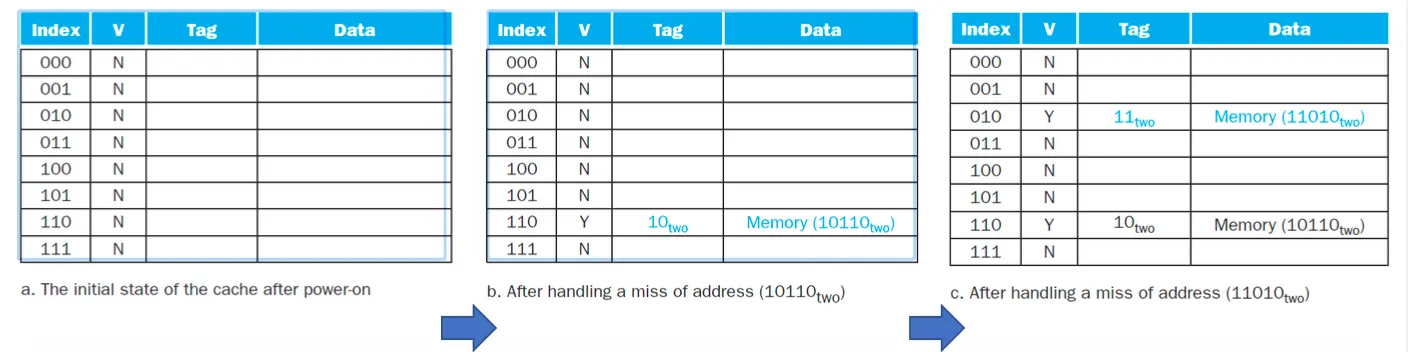

원하는 데이터가 cache에 존재하는지 아는 방법

- cache에 valid bit 추가

- valid bit: 엔트리가 유효한 주소를 포함하는지 판단하는 지표

- 초기값: 0, cache에 데이터가 저장되어 있으면 1

데이터가 cache에 존재한다면, 어떻게 찾는가?

- cache에 tag를 설정

- tag: 어떤 위치에서 왔는지 주소 정보를 포함 → 성(last name) 같은 것

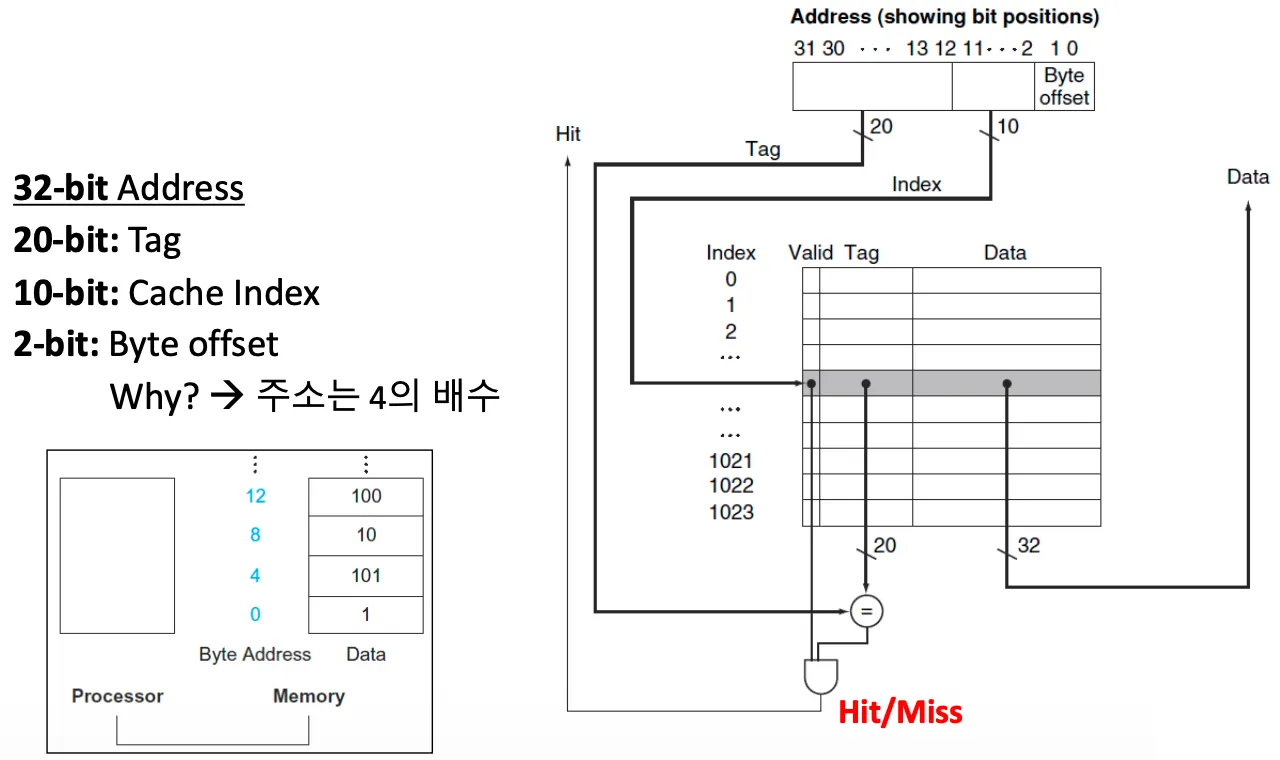

Example

1 word block

- Address(32 bits) = Tag(20 bits) + Cache Index(10 bits) + byte offset(2 bits)

- index를 이용

- index의 block에 valid bit + tag field의 일치 여부 확인

- 둘 다 1(AND gate)이면 hit

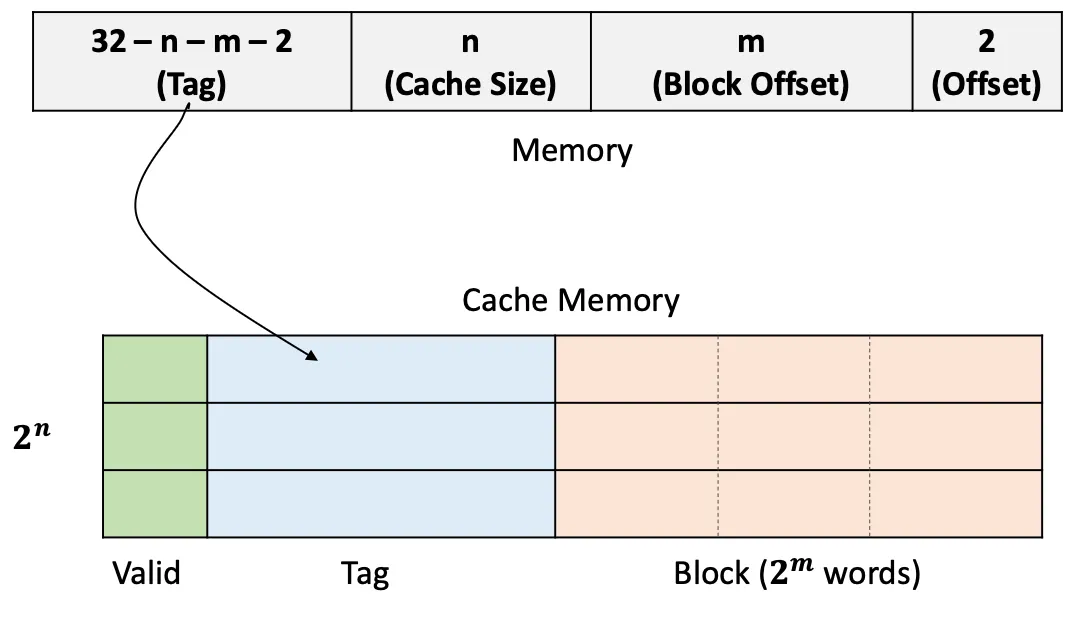

Larger block size

- 접근하려는 블록에 여러개의 워드 존재 → block size가 1보다 큰 경우

- Address(32 bits) = Tag(32 - n - m - 2 bits) + Cache Size(n bits) + Block Offset(m bits) + Offset(2 bits)

- Cache Size = 2^n개의 index 존재

- Block Offset = 2^m개의 words 가짐

Example

- 캐시가 64개 블록 사용, 한 블록당 16 bytes(=4 words) 저장

- Cache size = 2^n blocks = 64 blocks→ n = 6 bits

- Block Size = 2^m words = 2^(m+2) bytes = 16 bytes → m = 2 bits

16 KiB data, 4-word blocks 일 때, 얼마나 많은 bits가 필요한가?

- 총 데이터 bytes 수: 16 * 2^10 = 2^14 bytes

- 총 데이터 words 수: 2^14 / 4 = 2^12 words

- 총 블록(인덱스) 수: 2^12 / 4 = 2^10 blocks → Cache size n = 10 bits

- 한 블록 당 워드 수: 4 = 2^2 words → Block Offset m = 2 bits

- Tag: 32 - 10 - 2 - 2 = 18 bits

- 하나의 index 사이즈: valid bit(1) + tag(18) + words(4) * 32 = 147 bits

- 총 Cache 사이즈: 2^10 * 147 = 147 KiBits = 18.4 KiB

→ 약 1.15배 용량이 커짐

위와 동일, 16-words blocks일 때

- m = 4, n = 8

- block의 16개 words 중 MUX를 통해 block offset 값에 따라 하나를 찾음

64 blocks, block size 16 bytes일 때, 1200은 어디에 매핑되는가?

(Block address) modulo (Number of blocks in the cache)

- Block address: Byte address / Bytes per block = 1200 / 16 = 75

- 75 modulo 64 = 11번째 block

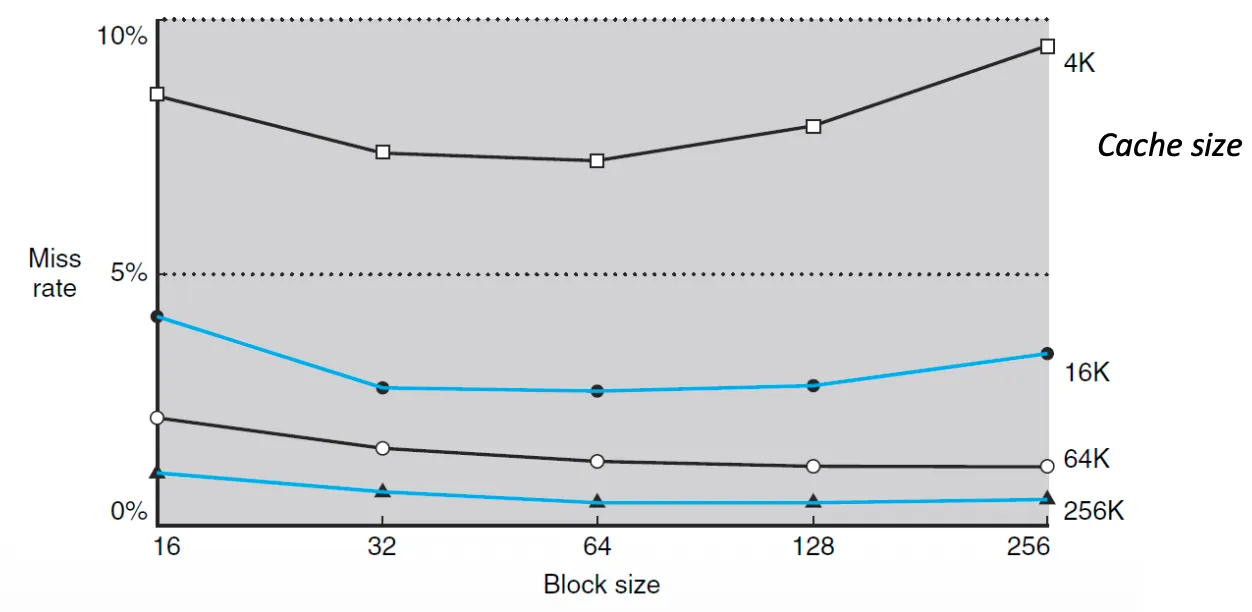

Miss Rate vs. Block Size

- Block size: 한 번에 가지고 오는 블록의 워드 개수/데이터의 크기

- Block numer: cache index

- block size가 커질수록 → spatial locality에 의해 miss rate 감소

- 하지만 일정 구간부터 miss rate 증가 → cache size가 고정이라면 block size가 커질수록 index는 감소 → 다양한 block을 가져오지 못함 → temporal locality에 의해 miss rate 증가

- cache size가 클 때 → index가 반으로 줄어도 원래 빈 공간이었을 확률 높음 → 성능 차이 거의 없음

- cache size가 커질수록 → index 개수 많아짐 → miss rate 감소

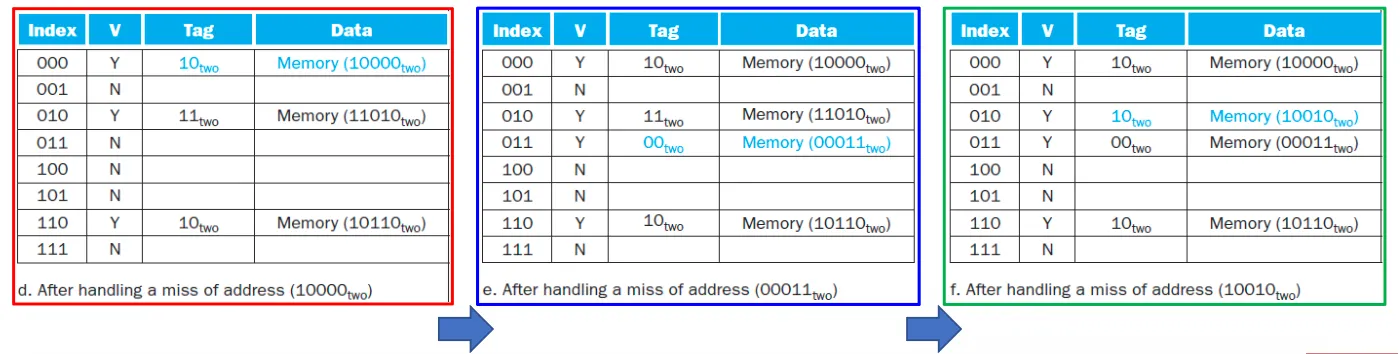

Handling Cache Misses

- PC에서 요청한 값을 메모리에 요청

- 해당 값을 가져오는 동안 기다림

- Writing: data를 cache memory에 올림 → tag field 작성 → valid bit 켜기

- cache memory에서 저장된 값을 cpu에 전달

Handling Writes

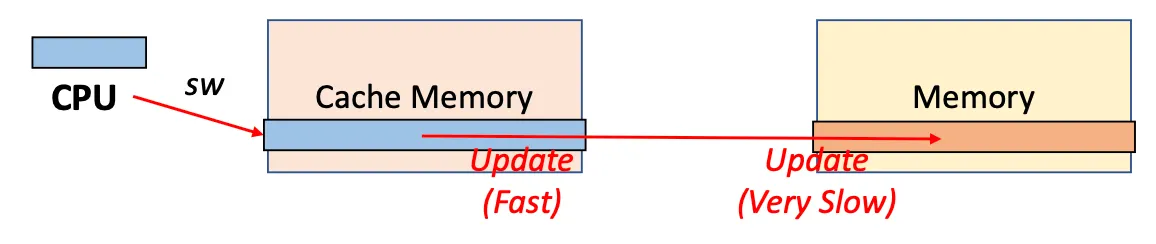

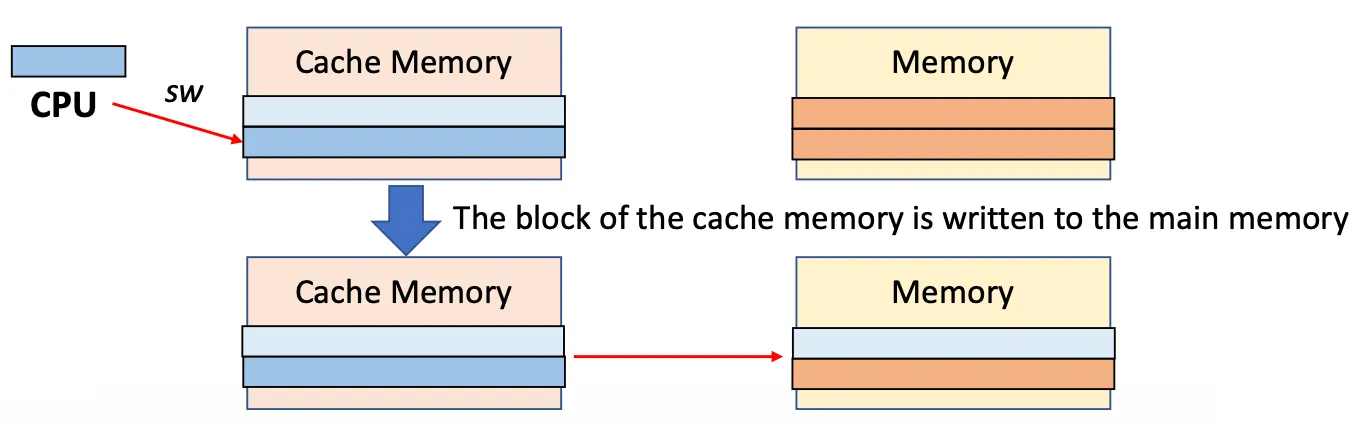

- sw를 수행했을 때, cache memory와 main memory 사이에 차이가 발생(inconsistent) → cache memory의 바뀐 값을 main memory로 옮겨야 함

1. Write-through

- cache memory에 sw하자마자(main memory와 차이가 생기기 전에) main memory도 업데이트

- main-cache 간 consistent하게 유지

- 성능상 좋지 않음

Use Write buffer

- cache memory에 sw가 적용되면, 해당 값을 write buffer로 전달

- write buffer에 차곡차곡 쌓다가 일정 순간에 main memory로 업데이트

- write buffer가 가득 차고, processor가 write 해야하는 상황 → write buffer가 empty 상태가 될 때까지 stall

2. Write-back

- block이 교체될 때 main memory로 입력

- Dirty bit: data가 modified인지 not modified인지 알려주는 indicator(1bit)

- 매번 업데이트되는 것이 아니라 교체될 때만 main memory에 접근 → 메모리 접근 효율 향상

728x90

반응형

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조] Lecture 19: Memory Hierarchy - Part3 (0) | 2026.02.12 |

|---|---|

| [컴퓨터구조] Lecture 18: Memory Hierarchy - Part2 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 15: The Processor - Part4 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 14: The Processor - Part3 (0) | 2026.02.12 |

| [컴퓨터구조] Lecture 13: The Processor - Part2 (0) | 2026.02.12 |